산업 전문가가 쓴 글이 아닙니다....!

#1. 웨이퍼 레벨 패키징이란

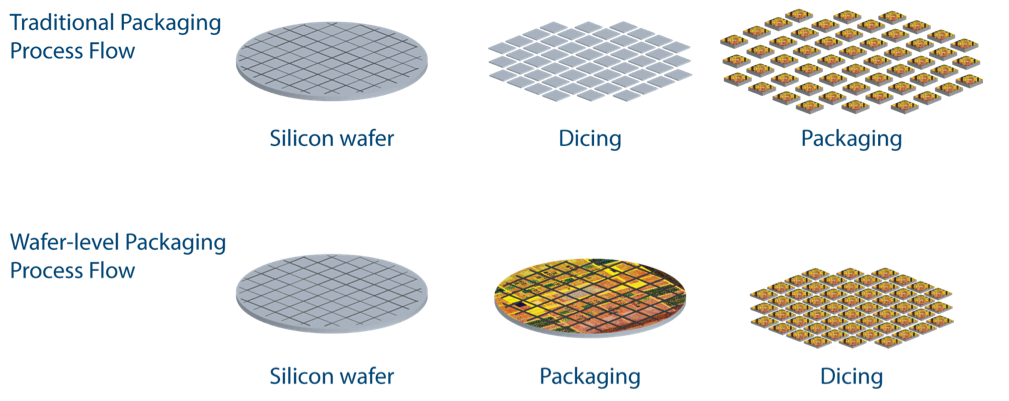

원래 패키징은 (1) 웨이퍼상에서 반도체 제작이 끝난 후 (2) 다이(Die)를 모두 자른 후 (Dicing) (3) 다이를 하나하나 패키징 하는 방식.

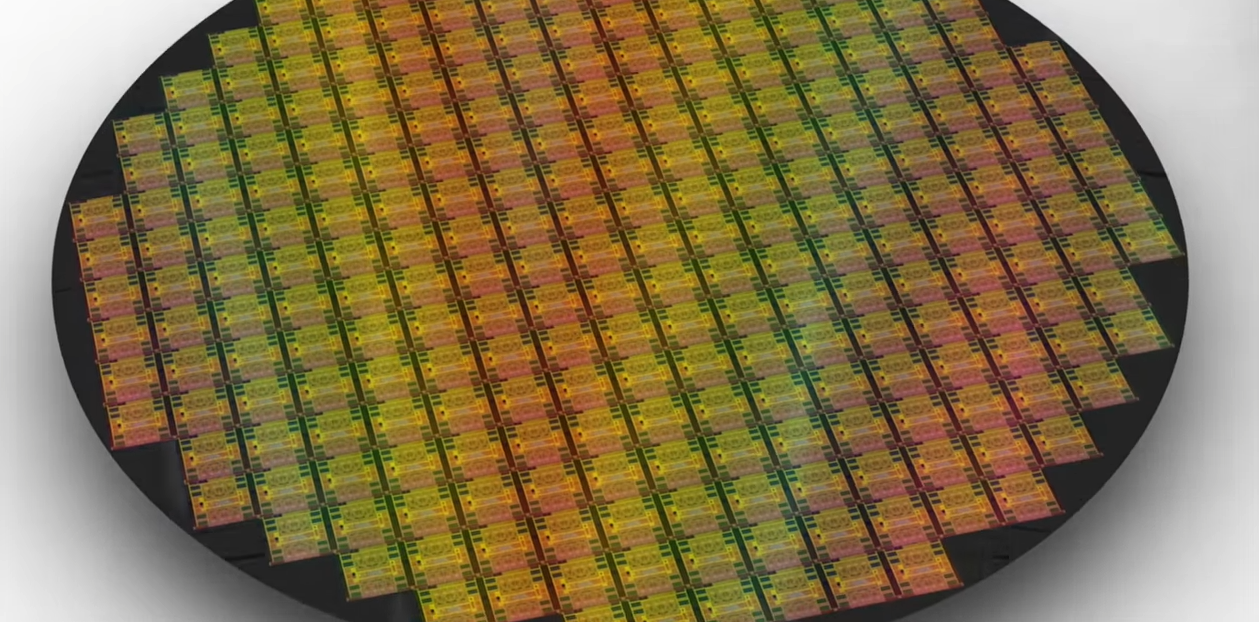

웨이퍼레벨 패키징은 웨이퍼 상에서 다수의 다이를 한번에 패키징 하는 것. 하나씩 떼어서 하던 것을 동시에 여러개를 하는 것이 웨이퍼 레벨 패키징의 특징. 웨이퍼 팹에서 하는 공정의 연장선상에 있다고 봐도 되고, 파운드리에서 사용하는 일반적인 공정과 장비를 사용한다. [출처: NXPI]

#2. 팬인-WLP(Fan-in Wafer Level Packaging)

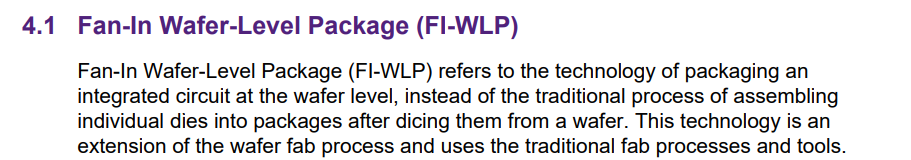

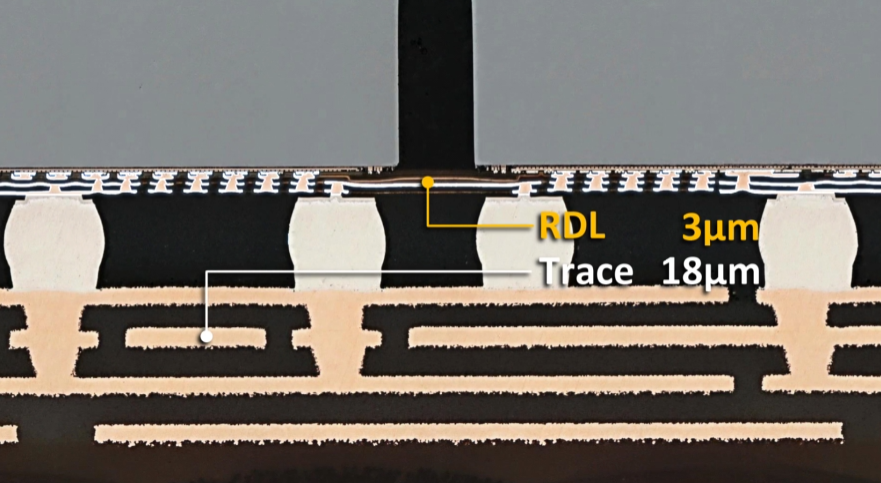

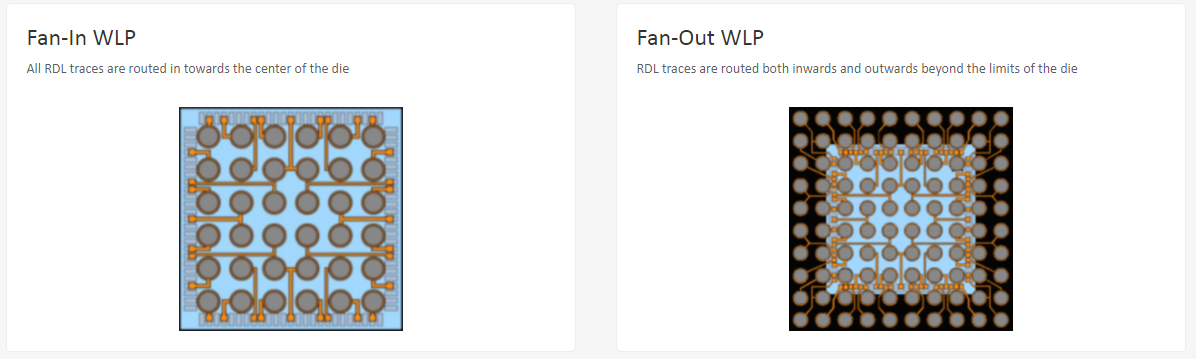

웨이퍼상에서 개별 다이를 자르기 전에, 한번에 패키징을 진행하는 것. 다른 패키징 방식들 처럼 반도체 기판(Substrate)를 따로 붙이는 것이 아니라, RDL(ReDistribution Layer)라는 일종의 회로를 웨이퍼에 인쇄한다. 그 위에 솔더볼을 붙여서 PCB와 접합하는 것. 그리고 패키징을 씌우고 칩을 잘라내는 방식이다.

팬인 WLP에서는 패키징이 끝난 후 칩을 잘라내니 패키지의 사이즈가 칩의 사이즈와 동일하다. 다만 그간 패키지가 수행하던 IC 칩 보호 기능이 조금 떨어질 것 같다는 생각이 든다. 상단만 보호가 가능하고, 웨이퍼를 잘라낸 측면은 보호가 덜 되는 것 아닌지....

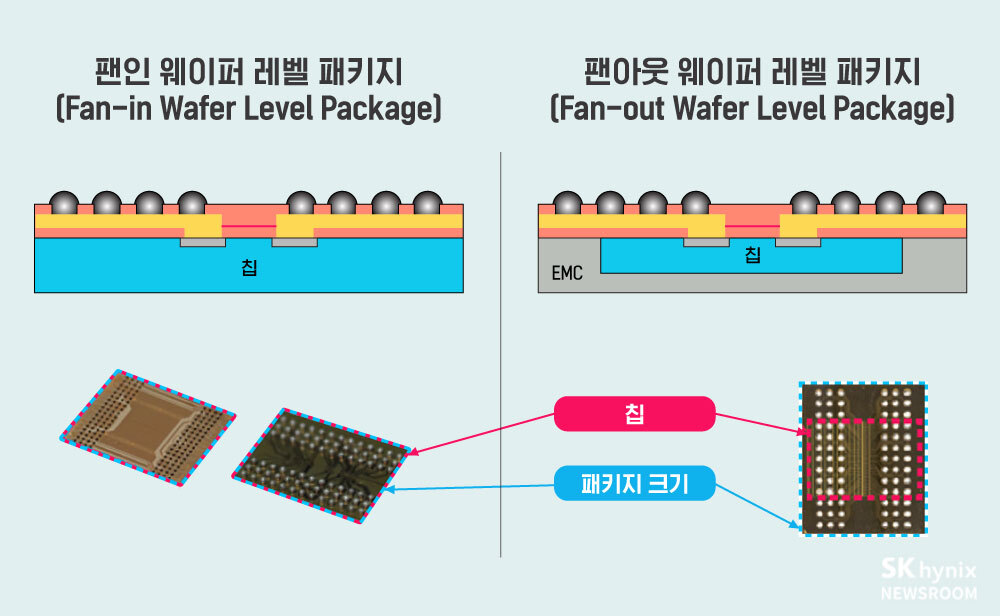

아래 영상이 Fan-In은 아니지만 RDL을 작업하는 과정. RDL이 어떤 식으로 제작되는지 대략적으로 감을 잡을 수 있다. (01:30) 영상 언급에 따르면 여기는 RDL-First 공법인 듯 하다. 후공정도 워낙 공법이 다양해서 일률적으로 기준을 두고 보기가 어려움.

이와같은 RDL은 PCB류의 Trace에 비해 훨씬 가늘게 설계된다.

#3. 팬아웃-WLP(Fan-out Wafer Level Packaging)

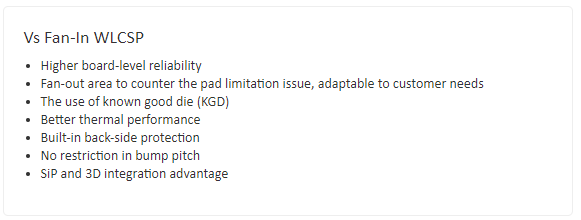

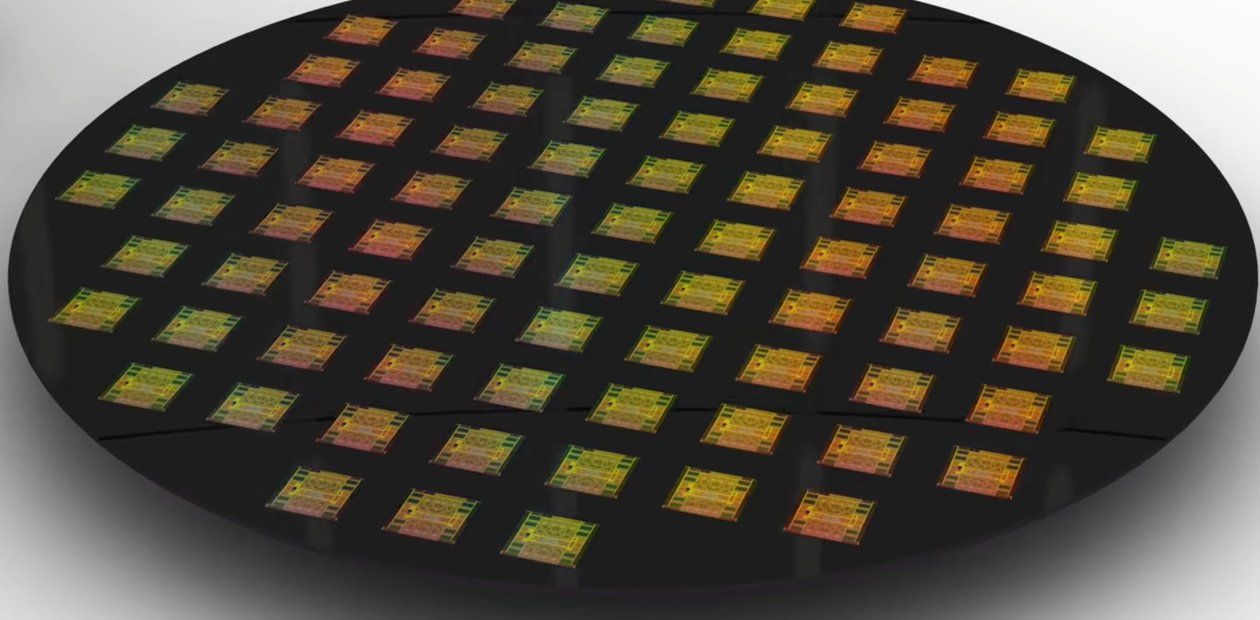

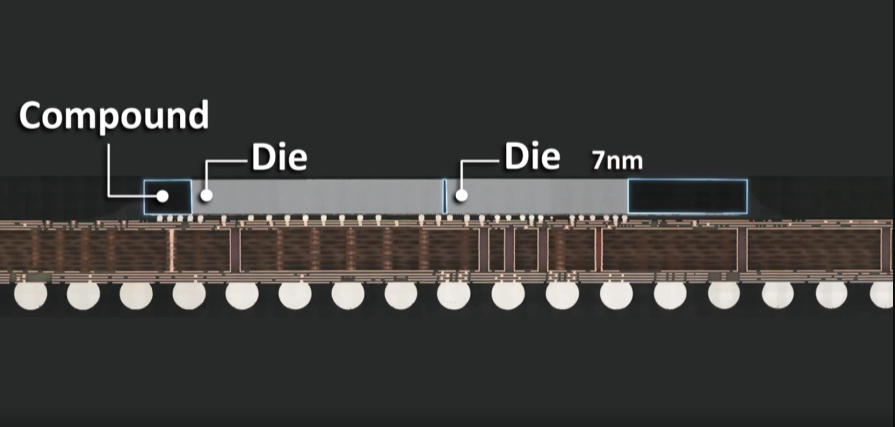

웨이퍼상에서 패키징을 한번에 진행하는데, Fan-In과 다른 점은 패키징 전에 다이를 먼저 잘라서 배치하는 작업을 한다. 이렇게 해서 사이에 공간이 생기니 (1) 칩 사이즈에 비해 더 넓은 I/O 면적을 확보할 수도 있고, (2) 웨이퍼 보호 면적이 넓어지니 Chip Reliaility도 높아진다. (3) 또한 불량 다이를 한번에 패키징 할 필요 없으니 단가 절감도 가능하다.

문제는, 다이를 잘라내고 이걸 다시 원형으로 재배치를 한다는건데. 잘라낸 후 배치도 정밀하게 해야 하고, 새로 배치한 다이가 공정 작업 중에 움직이거나 흔들리지 않아야 하는 등 난이도가 낮지 않다. 아래 동영상에 어떤 과정인지 시각적으로 볼 수 있다.

Fo-WLP의 다른 장점이라고 한다면, 이종간 패키징이 가능해 진다는 것. 서로 다른 크기와 기능을 가진 칩들을 하나의 패키지에 넣어서 포장할 수 있게 된다. 원판에 옮겨서 배치할 때 서로 다른 칩이 하나로 포장되도록 배치하면 되는 것.

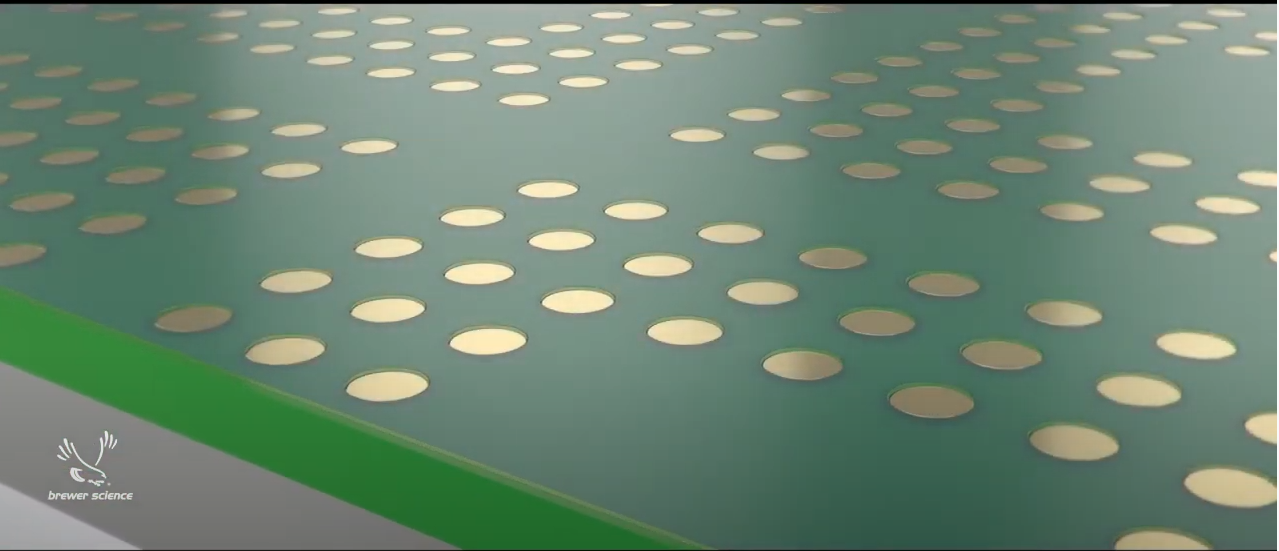

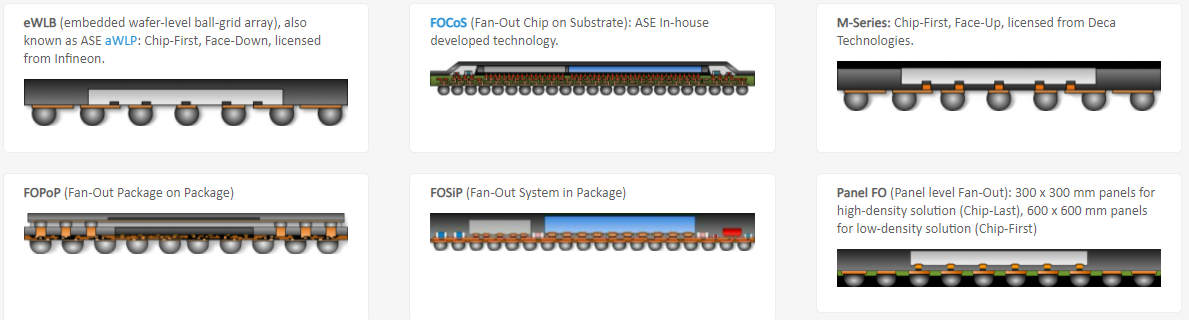

#4. PLP: Panel Level Packaging

웨이퍼 레벨 패키징에서는 원형 웨이퍼 상태에서 작업을 진행하는데, 개별 다이나 패키지는 사각형이고 원형 웨이퍼에서 작업을 하면 남는 공간이 생기게 된다. 따라서 이 단점을 극복하기 위해 시도하는 것이 사각형 패널 위에 올려 작업하는 PLP.

단순히 이론적으로 생각하면 PLP가 더 효율적인게 맞기는 한데, 공정 호환성을 생각하면 PLP의 단점이 보인다. 웨이퍼가 원형인 이유가 있는 것과 비슷하게 패키징에서도 원 형태에 기반한 장비랑 공정이 많은데, 갑자기 사각형에서 패키징 하면 공정 호환성이 떨어지게 된다. (WLP에서 배선하는데 사용하는 RDL도 사실상 노광/식각 작업을 통해 회로를 배선하는 작업이니) 물론 이 호환성을 극복하는 것이 기술력.

웨이퍼는 왜 다 원형일까

반도체 제조 공정을 보면 참 아까운 부분이 있다. 칩은 다 사각형으로 만드는데, 원형인 웨이퍼에 칩을 만들어서 (4)번으로 표기된 에지 다이(Edge die)들은 못 쓰는 것 들이라 전부 버린다. 그럴거

hunter-trader.tistory.com

일단 크게는 위에 기술한 것 처럼 나뉘기는 하는데, 회사마다 제품마다 그 공법이 매우 상이해서, 패키징 기술을 기계적으로 정리하는게 좋은 것 같지는 않다.

'산업 공부 > IT 하드웨어' 카테고리의 다른 글

| 메모리 반도체 약세 - 4분기 피크아웃인가... (0) | 2021.08.10 |

|---|---|

| 증착공정 - (2) CVD 증착방식 (0) | 2021.08.10 |

| 증착공정 - (1) 큰 분류와 PVD 증착방식 (0) | 2021.08.10 |

| 반도체 도핑 공정 - Ion Implantation / Diffusion (0) | 2021.07.27 |

| IC Substrate (반도체 기판) vs PCB의 차이 (0) | 2021.07.18 |

| 전력반도체 모듈과 이산소자 (0) | 2021.07.06 |

| 아날로그 반도체의 특징 (0) | 2021.06.08 |

| 반도체 산업 관련 주요 지표 정리 (0) | 2021.06.04 |